Imperas Videos

DVCon2022 Tutorial on the 5 levels of RISC-V Processor Verification

DVCon 2022

Abstract:

The RISC-V open standard ISA (Instruction Set Architecture) offers developers the opportunity to configure the features and functions of a custom processor to uniquely address their target end application needs and requirements. RISC-V has a modular structure with many standard instruction extensions for additional dedicated hardware features such as Floating Point, Bit Manipulation, DSP, Cryptographic, Vectors, and many others currently under development. In addition, custom instructions can be added to further optimize the design. This tutorial covers some of the options and latest trends in simulation-based RISC-V processor verification based on industry standards with UVM and SystemVerilog test benches. With an in-depth review of the new open standard RVVI (RISC-V Verification Interface), this tutorial will include examples of RISC-V test benches with leading EDA tools and SoC DV flows adapted for the complexities of RISC-V processor verification. Starting with entry level, and basic trace compare followed by a detailed review of the latest approaches with Data-path lockstep-compare and Asynchronous lockstep-compare. Examples will be shown based on some popular open-source cores, including a comparison of the different DV methods and options.

Speaker: Simon Davidmann – Imperas Software

Speaker: Lee Moore – Imperas Software

The PDF of the slides used in this talk are available at this link

This DVCon presentation can be viewed on the YouTube channel for Imperas here.

DVCon 2022: Introduction to RISC-V CPU design verification

DVCon 2022

Abstract:

With all the design flexibility and innovations supported by the open standard ISA of RISC-V, quality processor verification is now another flexible option. This talk gives an introduction and overview of the Imperas presentations and announcements at DVCon 2022.

Speaker: Kevin McDermott – Imperas Software

The PDF of the slides used in this talk are available at this link

This DVCon presentation can be viewed on the YouTube channel for Imperas here.

DVCon 2022: Imperas RISC-V Design Verification solutions

DVCon 2022

Abstract:

With a history based in EDA tools and background of SystemVerilog, the Imperas technology is now at the forefront of RISC-V processor verification.

This talk gives an overview of the Imperas solutions for RISC-V verification including examples of the methods used by customers and users on several projects.

Speaker: Larry Lapides – Imperas Software

The PDF of the slides used in this talk are available at this link

This DVCon presentation can be viewed on the YouTube channel for Imperas here.

Introduction to RISC-V processor verification methodology with dynamic testbench for asynchronous events

SemIsrael Tech Webinar, February 22 2022

Abstract:

For SoC designers adopting RISC-V, tackling the processor DV tasks presents some new challenges. The established SoC flows have some standard assumptions – test benches written for UVM SystemVerilog flows and known good processor IP from a mainstream supplier. The availability of open-source RISC-V cores and the growing interest to add custom extensions are all increasing the DV tasks.

The basic RISC-V compliance suite is insufficient to achieve the coverage requirements for a complete DV test plan, and comparison-based testing with predicted results has built-in limitations. The latest work on dynamic test benches allows the processor RTL to be subjected to the full range of asynchronous events and debug operations. Interactive dynamic test benches allow both detection of issues and also efficient investigation for a timely resolution. This talk will present the latest results from extensively testing some popular open-source cores, including discussion of a new open standard for test bench interfaces.

Speaker: Larry Lapides – Imperas Software

The PDF of the slides used in this talk are available at this link

This presentation can be viewed YouTube.

Keynote: Are the RISC-V design freedoms leading to RISK in Verification quality?

RISC-V Summit 2021

Abstract:

Traditional SoC projects estimate that 50-80% of the cost/effort will be for verification, but that is based the traditional approach using mainstream providers with pre-verified processor IP cores. RISC-V offers more options to SoC Developers, from developing a custom core, downloading an open-source project, selecting from one of the new IP providers, plus adding custom instructions to any of these starting points.

The flexibility of RISC-V appears to imply an increase in the DV scope of work for any SoC project with a customized RISC-V core, in this talk we will introduce the Imperas Reference Model based solutions for RISC-V processor verification.

Speaker: Larry Lapides – Imperas Software

The PDF of the slides used in this talk are available at this link

This RISC-V Summit 2021 presentation can be viewed on the RISC-V YouTube channel here.

Lightning talk: Open-Source RISC-V Cores with Industrial strength verification

RISC-V Summit 2021

Abstract:

This case study explores the background, development and implementation of the OpenHW verification environment for CV32E40P known as “core-v-verif”. Since the goal of the project is to support adoption on of an open-source IP core, the initial deliverable quality is not the only concern. One attractive aspect of an open-source core is the potential for adopters to modify, adapt, or extend the base core features. Thus, the verification plan needs to anticipate the future use case with flexibility built in to the testbench to accommodate future modifications as adopters extend the core features.

Speaker: Simon Davidmann – Imperas Software

Speaker: Lee Moore – Imperas Software

The PDF of the slides used in this talk are available at this link

This RISC-V Summit 2021 presentation can be viewed on the RISC-V YouTube channel here.

Keynote: Is hardware/software co-design for applications now a reality with RISC-V?

RISC-V Summit 2021

Abstract:

RISC-V Vector instructions offer significant flexibility and options to configure a hardware accelerator for applications such as Datacenters and AI. Following initial cloud-based development with extensive real-world datasets, the migration to a hardware accelerator array with RISC-V vectors is redefining the software driven approach to hardware design.

This talk highlights SoC architectural exploration with multicore arrays and optimized RISC V processors to support early software development for vector accelerators. It introduces some of the challenges and discusses different approaches being adopted in the community/industry.

Speaker: Kevin McDermott – Imperas Software

The PDF of the slides used in this talk are available at this link

This RISC-V Summit 2021 presentation can be viewed on the RISC-V YouTube channel here.

Brief introduction to the 5 levels of RISC-V processor verification

RISC-V Summit 2021

Abstract:

The open RISC-V Instruction Set Architecture (ISA) is enabling a wide range of options on the design side, to completement this a number of options can be applied to the verification tasks, since a basic proof of concept prototype may not need all the quality checks as a high volume or high reliability application. This talk will review the 5 different simulation-based DV flows, ranging from simple signature-based comparisons for architectural validation to advanced ‘step-and-compare’ flows that support the most complex processors.

Speaker: Kevin McDermott – Imperas Software

The PDF of the slides used in this talk are available at this link

This RISC-V Summit 2021 presentation can be viewed on the RISC-V YouTube channel here.

Software design: porting software to RISC-V using Imperas Virtual Platforms

RISC-V Summit 2021

Abstract:

While much of the focus and energy of the RISC-V adopters has so far gone into the development of the RISC-V architecture and specific cores, the real success of RISC-V is dependent upon the key software tasks for new applications, porting legacy software, and optimising OS/RTOS ports and drivers for the wide range of RISC-V devices being built. With more custom silicon projects starting every day, virtual platforms (often called virtual prototypes) offer a viable alternative to hardware prototypes for software engineering tasks.

This talk will highlight how simulation and virtual platforms can be used for software development for new processors and SoCs including a demonstration with Quake running on RISC-V.

Speaker: Katherine (Kat) Hsu – Imperas Software

Speaker: Manny Wright – Imperas Software

The PDF of the slides used in this talk are available at this link

This RISC-V Summit 2021 presentation can be viewed on the RISC-V YouTube channel here.

DVCon 2021. A personal perspective on the history of SystemVerilog and Superlog

Simon Davidmann, Imperas, hosts a personal perspective on the formation and history of SystemVerilog with the co-founders of Verilog and SystemVerilog. In 1997, Co-Design Automation Inc., was set-up by Simon Davidmann and Peter Flake, to design and implement a new language and simulator. Phil Moorby joined in 1999. The company name showed the desire to include software/hardware co-design, but there was more customer interest in hardware design and verification, and even system specification. Their original vision of Superlog (derived from Super and Verilog) was to have a single language for system specification, hardware design, hardware verification, and software development. Superlog was later renamed to SystemVerilog as it became adopted by Accellera and later became an IEEE standard.

The paper referenced in the video is available at this link on this link.

DVCon 2021. 25 years after Verisity, verification is still evolving

Larry Lapides, Imperas, hosts a retrospective review on the impact of Verisity (now Cadence Specman) and the continuing evolution of advanced semiconductor SoC verification over the past 25 years. The guests include Bryan Dickman, co-founder of Valytic, a former ARM verification engineer and Specman user. Plus, Sean Smith of Esperanto, ex-Cisco DV lead, and also an early Specman user. As design complexity continues to increase the verification tools and methodologies have evolved to address to scale of modern SoC designs, but looking back offers an interesting in sight on how DV teams approach the adoption of new tools and techniques.

Webinar on Optimizing RISC-V custom instructions with software driven analysis and profiling

Imperas presentation on "Optimizing RISC-V custom instructions with software driven analysis and profiling" by Kevin McDermott, VP of Marketing at Imperas Software, as part of a Webinar together with Andes Technology and UltraSoC Technologies on September 29 2020.

This Webinar is on the flexibility of RISC-V in SoC designs for 5G, AI, AR/VR, and IoT with optimized extensions and custom instructions. Starting with architectural exploration to profile applications and identify candidate instructions, then details of the design flow to implement and verify new extensions, and use on-chip instrumentation for debug, plus analysis and lifecycle management aspects.

RISC-V is opening up new design freedoms with optimized solutions beyond the boundary of standard processor core roadmaps. Domain specific optimizations offer just the right balance between hardware efficiency and software flexibility.

Start exploring your next project with the flexibility of RISC-V and optimized extensions.

Includes a live Q&A session after the presentations.

This webinar can be viewed on this link. (Requires registration.)

NSITEXE Inc. Denso: Vector Compliance Testing for RISC-V - Hideki Sugimoto and Koji Adachi

NSITEXE presentation on "Vector Compliance Testing for RISC-V" by NSITEXE Inc. (Denso subsidiary) by Hideki Sugimoto - CTO, and Koji Adachi - CPU Architect, with guest speaker Simon Davidmann, CEO at Imperas, at the RISC-V Global Forum during the virtual event on September 3 2020.

The first step to testing a RISC-V vector instruction implementation is to test compliance to the specification. To do this requires both compliance tests and a reference model. NSITEXE, with its Data Flow Processor (DFP) IP block, required such testing for its implementation of the vector engine. The Imperas RISC-V ISS, riscvOVPsim, is in use as the reference model for the Imperas RISC-V Vector Compliance Test Suite (CTS). Imperas has developed a Directed Compliance Test Generator, which achieves over 95% functional instruction coverage with those tests generated. Using the Vector CTS for the NSITEXE configuration has enabled confirmation of compliance with v0.8 of the RISC-V vector specification.

This paper discusses the NSITEXE DFP vector engine implementation, the generation of the Vector Compliance Tests for the NSITEXE configuration and the results of those tests including coverage data.

This RISC-V Global Forum presentation can be viewed on the YouTube channel for RISC-V here.

OpenHW CORE-V Verification Test Bench - Commercial Quality Verification of Open-Source RISC-V Core

OpenHW Group presentation on "CORE-V Verification Test Bench - Commercial Quality Verification of Open-Source RISC-V Core" by Rick OConnor, CEO at OpenHW Group, Aimee Sutton, Engineer at Metrics Technologies, and Simon Davidmann, CEO at Imperas Software, at the RISC-V Global Forum during the virtual event on September 3 2020.

High quality verification is crucial to any HW IP development and in particular for open-source processor cores. Industry quality, coverage driven verification is essential and it is leveraging commercial tools, flows and simulators. These are "must haves" in order for open-source IP to be adopted by leading semiconductor companies for use in high volume SoCs.

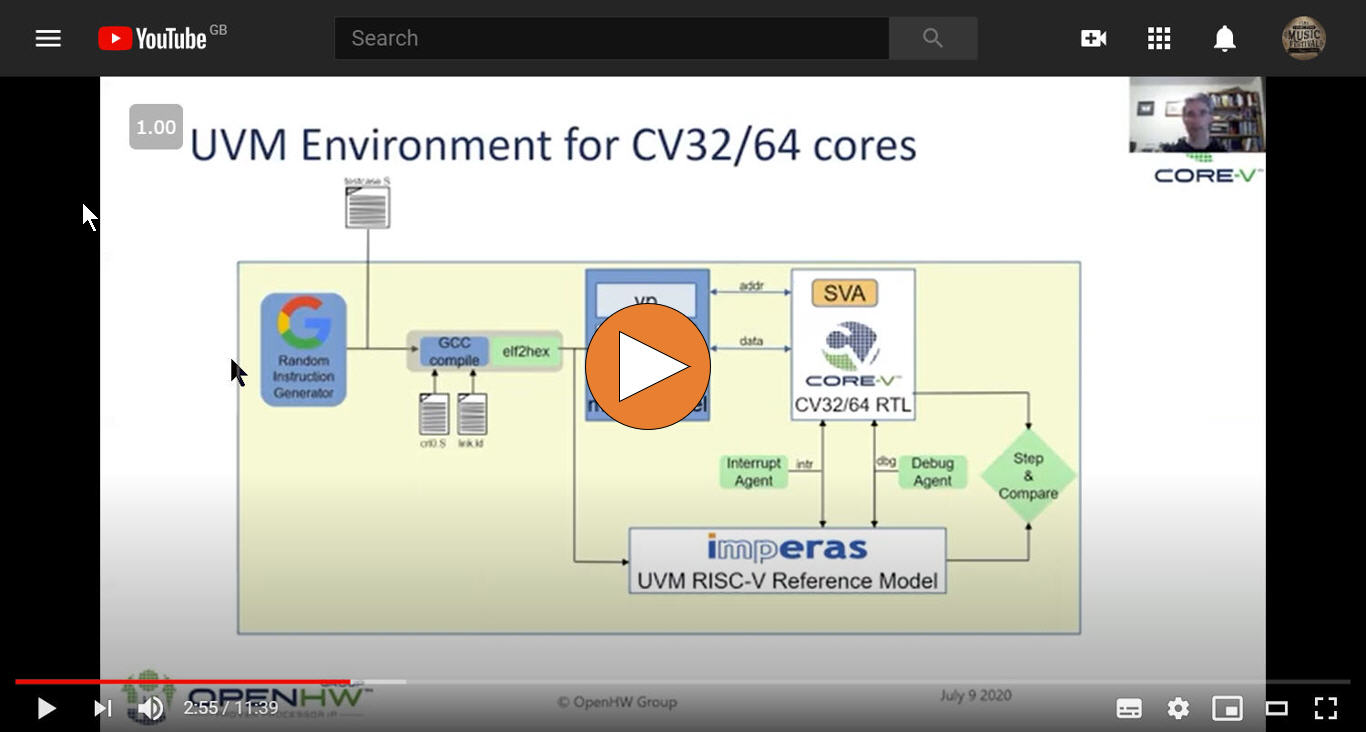

This talk provides details of the CORE-V Verification Test Bench, an open-source "step & compare" System Verilog / UVM environment built by the OpenHW Group ecosystem leveraging the Imperas RISC-V Golden Reference Model and the Metrics Cloud-based EDA Platform.

This RISC-V Global Forum presentation can be viewed on the YouTube channel for RISC-V here.

Verifying all the flexibility of RISC-V within SoC DV test plans

Imperas presentation on "Verifying all the flexibility of RISC-V within SoC DV test plans" by Simon Davidmann, CEO at Imperas, at the RISC-V Global Forum during the virtual event on September 3 2020.

One of the attractive features of RISC-V is the ability to add, and with ecosystem support, new optimized instructions and extensions to a processor implementation. At first it appears as simple task to look at opportunities in the application code that could be accelerated with some dedicated new hardware. However, since hardware typically has a much longer life cycle than software, future updates and roadmap needs must be anticipated. Thus, the art of ISA design is using fine grain analysis to accelerate just the key steps while leaving sufficient flexibility to support new software updates and advances.

While in multi-core arrays a custom extension can offer a lightweight communication channel between processors. This extends the scope beyond the processor itself into system design and analysis. This talk illustrates the key profiling and analysis steps for custom extensions.

This RISC-V Global Forum presentation can be viewed on the YouTube channel for RISC-V here.

Optimizing RISC-V custom instructions with software driven analysis and profiling

Imperas presentation on "Optimizing RISC-V custom instructions with software driven analysis and profiling" by Lee Moore and Duncan Graham, Senior Applications Engineers at Imperas, for the RISC-V Global Forum during the virtual event on September 3 2020.

One of the attractive features of RISC-V is the ability to add, and with ecosystem support, new optimized instructions and extensions to a processor implementation. At first it appears as simple task to look at opportunities in the application code that could be accelerated with some dedicated new hardware. However, since hardware typically has a much longer life cycle than software, future updates and roadmap needs must be anticipated.

Thus, the art of ISA design is using fine grain analysis to accelerate just the key steps while leaving sufficient flexibility to support new software updates and advances. While in multi-core arrays a custom extension can offer a lightweight communication channel between processors. This extends the scope beyond the processor itself into system design and analysis.

This RISC-V Global Forum presentation can be viewed on the YouTube channel for RISC-V here.

Meetup: RISC-V DV: The Most Important Task

Imperas presentation on "RISC-V DV: The Most Important Task" by VP of Sales at Imperas, at the RISC-V virtual Meetup event held on July 22 2020.

Imperas are the guest host for the RISC-V Israel Meetup event and included talks by WD and Syntacore. The Imperas talk focused on the most critical design challenges for SoC adopting RISC-V and the latest updated on the RISC-V Processor DV.

This Meetup video can be viewed on YouTube here.

Extending SoC Design Verification Methods for RISC-V Processor DV - Article and video presentation

During the virtual DAC 2020 event Mentor hosted the traditional verification academy talks online.

Imperas presented "Extending SoC Design Verification Methods for RISC-V Processor DV" by Simon Davidmann, CEO at Imperas, at the Mentor Verification Academy event during the virtual event for DAC 2020.

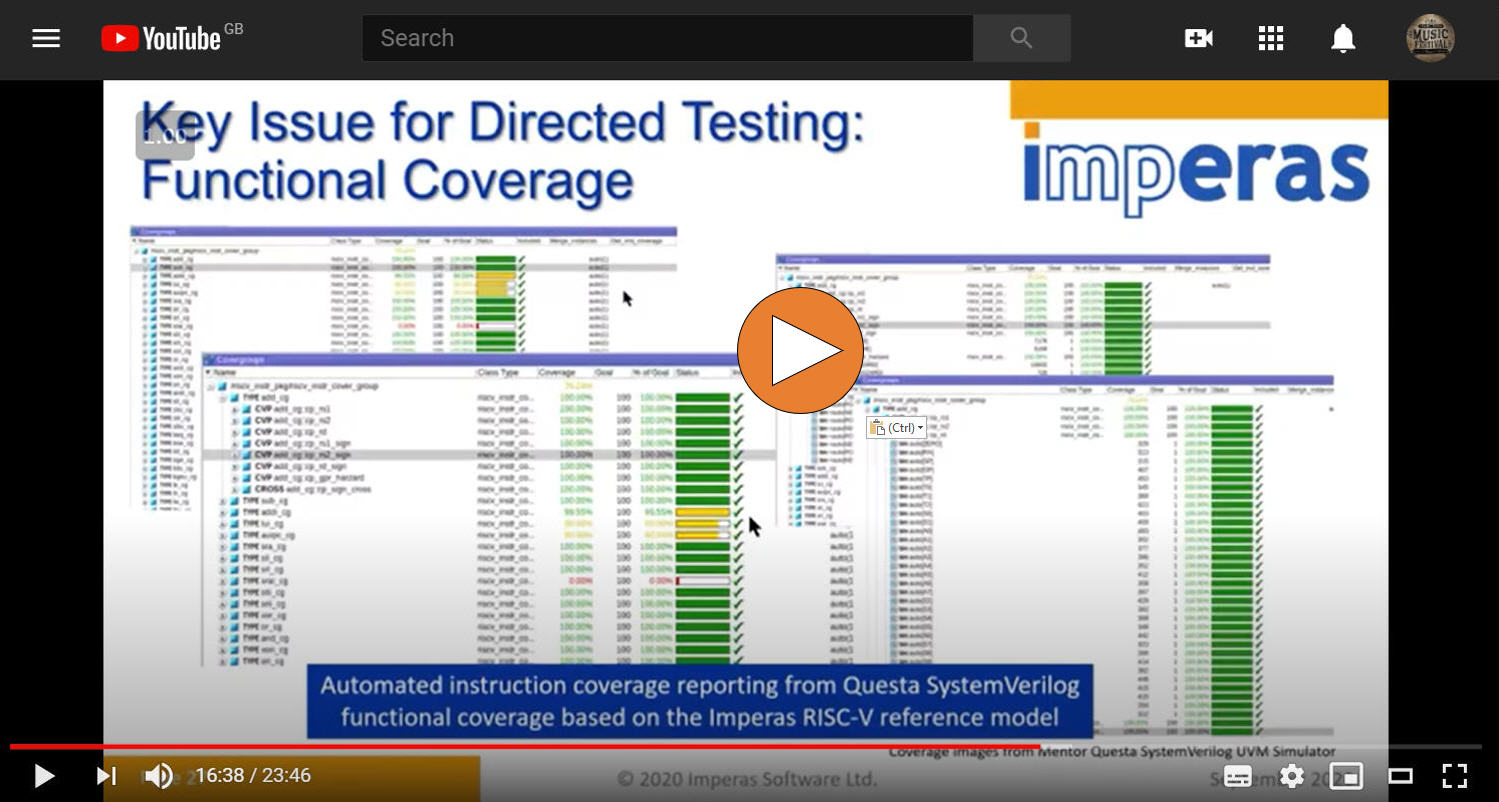

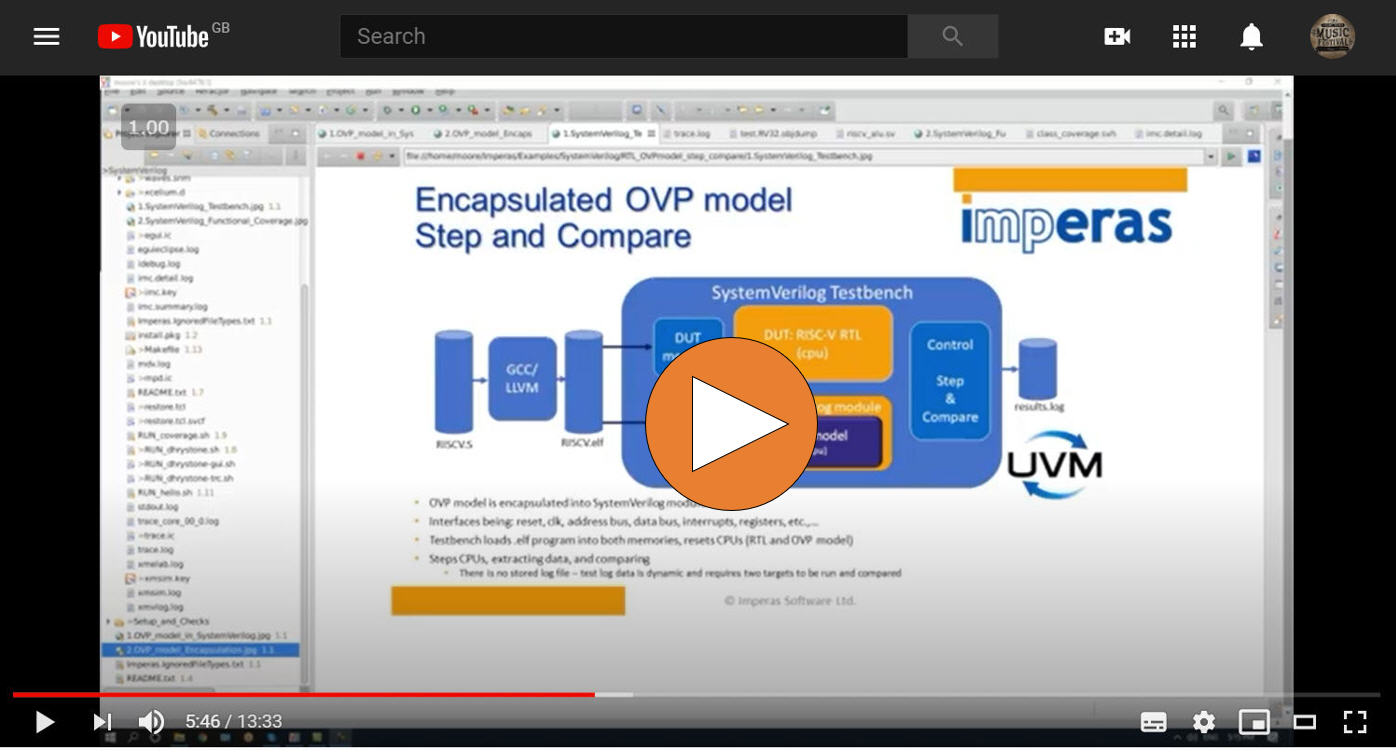

As SoC developers adopt RISC-V and the design freedoms that an Open ISA (Instruction Set Architecture) offers, DV teams will need to address the new verification challenges of RISC-V based SoCs. The established SoC verifications tasks and methods are well proven, yet depend on the industry wide assumption of "known good processor IP". However, the new DV challenges are not purely focused on the processor IP. Since an Open ISA allows much greater design freedom, the impact extends well into the SoC itself. Mentors Questa is fundamental to the RISC V processor verification with the RTL of the processor DUT (Device Under Test) and a RISC-V golden reference model encapsulated in the SystemVerilog UVM testbench allows step-and-compare testing.

This talk outlines the new test methods including instruction stream generators, reference models and SystemVerilog testbenches for Questa and includes results from testing some popular open source RISC-V cores.

The written paper and video can be viewed at the Mentor Verification Horizons site on this link.

Valtrix and verification of RISC-V Open ISA cores

Presentation on "Verification of RISC-V Open ISA processors - Testing functional correctness for the latest extensions for Bit Manipulation and Vectors." by Shubhodeep Roy Choudhury, Managing Director & Co-founder at Valtrix Systems, at the RISC-V pavilion during the virtual event for DAC 2020.

The RISC-V Vector extensions are designed to support complex arithmetic operations required for applications involving linear algebra, such as supercomputers, cryptography, AI, ML and deep learning (DL). A traditional or scalar ISA is based around operations on single data items, a Vector processor operates over an array of data items which enables acceleration of key computational workloads.

This talk, presents the different mechanisms and methodologies employed in the design verification flow to test the functional correctness of vector and bit manipulation extensions and interoperability with other extensions and privilege mode of execution in open source and commercial RISC-V designs.

Due to pressures of the market opportunity and potential for RISC-V Vector implementations, RTL level designs are tracking the specification revisions which in turn require the test plan to adapt to the evolving requirements. Latest status updates and results of the current work in progress will be presented.

This DAC presentation can be viewed on the YouTube channel for DAC TV here.

OpenHW and verification of RISC-V Open ISA cores

OpenHW presentation on "Verification of Open RISC-V cores: Adding value to the CORE-V Family of open source processor cores" by Mike Thompson, Director of Engineering, Verification Task Group at OpenHW Group, at the RISC-V pavilion during the virtual event for DAC 2020.

While open source processor IP cores have some attractive qualities, concerns on verification remain a key barrier to adoption. At OpenHW group the members and supporters are addressing the verification of the CORE-V family of open source processor cores using industry standard tools and flows.

This talk with share the details of the SystemVerilog UVM methodologies based on a reference model encapsulation for step-and-compare testing, and the use of the open source Google Instruction Stream Generator. With the latest coverage results and analysis, this talk will highlight the process within the Verification Working group with co-chairs supported by Futurewei Technologies, Inc. and Silicon Labs.

This DAC presentation can be viewed on the YouTube channel for DAC TV here.

Verification of RISC-V Open ISA processors using Imperas

Imperas presentation on "Verification of RISC-V Open ISA processors: New Freedoms in Design Require New and Improved Verification Methodologies" by Lee Moore and Simon Davidmann, of Imperas, at the RISC-V pavilion during the virtual event for DAC 2020.

The RISC-V community using Open Source and/or commercial cores need to consider the test plans for a many-core SoC based on Open ISA processors, all of which may be different in any number of ways - from implementations with micro-architectural distinctions, to optional features and optimized custom instructions.

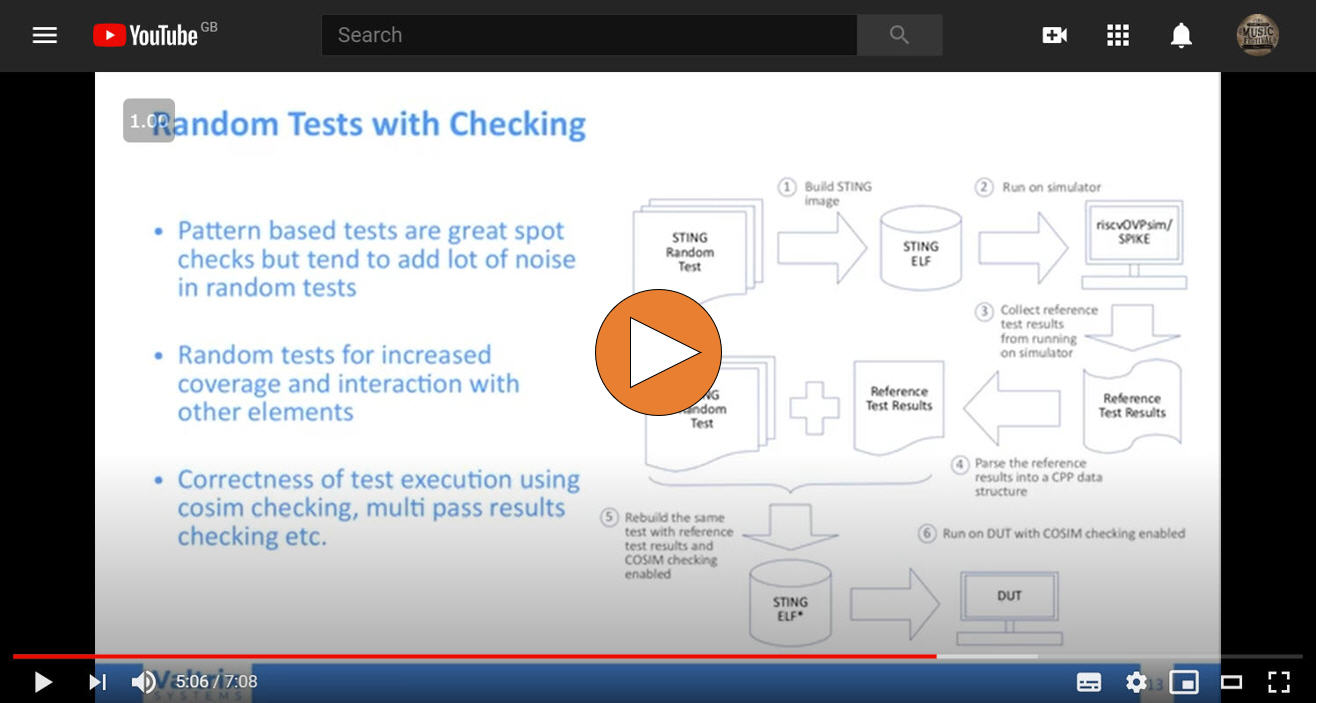

A test plan requires 4 things - a design to test, a DV plan, some tests to run and a reference to compare against. Compliance is the essential baseline test for an Open ISA implementation, but coverage frameworks and methods help define the quality metrics of progress within the complete processor DV plan. Random instruction testing offers the potential to explore the design state in challenging and unexpected ways, the art of the test comes from focused attention across corner case scenarios. This talk covers the latest updates and methods for coverage analysis and reference model-based verification.

This DAC presentation can be viewed on the YouTube channel for DAC TV here.

What is next for RISC-V Vectors, Verification, and Value-added Extensions

Imperas presentation on "What is next for RISC-V Vectors, Verification, and Value-added Extensions" by Simon Davidmann, CEO at Imperas, at the RISC-V pavilion during the virtual event for DAC 2020.

This extensive and in-depth update includes an Imperas company overview, and covers the use of virtual platform and simulation throughout the design cycle from early architectural exploration, through processor DV to software development.

This DAC presentation can be viewed on the YouTube channel for DAC TV here.

Webinar on RISC-V and SoC Architecture Exploration - Quick Start demo of early design phase prototypes

Imperas presentation on "RISC-V and SoC Architecture Exploration for AI and ML Many-core Compute Arrays: Quick Start demo of early design phase prototypes" by Kevin McDermott, VP of Marketing at Imperas Software, as part of a webinar together with Andes Technology and UltraSoC Technologies on July 15 2020.

Webinar on the key hardware and software prototyping phase, including demos with example platforms to test multicore processing elements, which are the foundational building blocks of AI Inferencing or ML designs. The Imperas presentation and demonstration highlights "Virtual Platforms as early evaluation & demo boards - Early software development including debug and verification". Includes a Q&A session after the presentations and demonstrations.

This webinar can be viewed on this link. (Requires registration.)

OpenHW TV Episode 1: RISC-V Processor Verification

The first episode of OpenHW TV focused on the Verification of CORE-V open source RISC-V processor IP cores. Guests include the new Co-Chairs of the OpenHW verification task group (Futurewei and SiliconLabs) with contributing members Imperas Software and Metrics Technologies highlighting the open CORE-V processor IP Design Verification (DV) plan using state of the art flows and SystemVerilog UVM testbenches with encapsulated Imperas RISC-V reference model, coverage-based flow, and Metrics flexible cloud-based environment. Includes a Q&A session after the updates and presentations.

The video can be viewed here.

Exploring Next Generation SoC Architectures with Virtual Platforms and RISC-V

Imperas presentation on "Exploring Next Generation SoC Architectures with Virtual Platforms and RISC-V" by Kevin McDermott, VP of Marketing at Imperas, at the SemIsrael Virtual Technology Week 2020, June 15-17 2020.

As SoC designers explore new architectural approaches with multi-processor configuration and arrays, virtual platforms allow rapid design options and support full application software development to fine tune and test new multi-processor structures with development iterations at the speed of software. RISC-V adds new dimensions of processor flexibility with many options and configurations plus custom instructions. Using software driven design methodologies allows profiling and analysis of new extensions for domain specific applications. The new RISC-V vector extension help support complex arithmetic operations required for applications involving linear algebra, such as supercomputers, cryptography, AI, ML and deep learning (DL). As RISC-V processor are adopted within SoCs, the full design verification (DV) process can be supported with SystemVerilog test benches and reference model-based verification, including the latest work with Google Instruction Stream Generator, compliance suite, and directed tests.

The video can be viewed here.

Webinar on RISC-V and SoC Architecture Exploration for AI an ML ManyCore Compute Arrays

Imperas presentation on "RISC-V and SoC Architecture Exploration for AI and ML Many-Core Compute Arrays" by Kevin McDermott, VP of Marketing at Imperas, as part of a webinar together with Andes Technology and UltraSoC Technologies on May 6 2020.

This webinar covers the latest challenges designers are facing when accelerating AI/ML application with custom SoCs and RISC-V. Artificial Intelligence (AI) and Machine Learning (ML) are among the fastest growing market segments as designers look to optimize domain specific SoC devices to accelerate complex algorithms and applications. While highlighting the latest examples for these applications many of the techniques and insights can equally be applied to any RISC-V based SoC design.

The webinar covers the key SoC design stages of: (1) Architectural exploration: Software driven prototype analysis with virtual platforms. (2) RISC-V core configuration: Optimized features for cores and processor sub-systems. (3) Full on-chip instrumentation: Debug and trace, plus on-chip performance monitors. Concludes with a Q&A session after the presentations and demonstrations.

This webinar can be viewed on this link. (Requires registration.)

Meetup: RISC-V Models for Architecture Analysis, Software Development and DV

Presentation on "RISC-V Models for Architecture Analysis, Software Development and DV" by VP of Sales at Imperas Software, at the RISC-V virtual Meetup event held on April 2 2020 with Andes Technology.

This Meetup video can be viewed on YouTube here.

RISC-V at Embedded World 2020: Imperas Presentation

Imperas presentation on "RISC-V Processor Verification and Extensions with Custom Instructions" by Kevin McDermott, VP of Marketing at Imperas, at the RISC-V booth during Embedded World Exhibition and Conference in Nuremberg, Germany.

Covering a range of topics on RISC-V and Imperas contributions to RISC-V with customers, adopters and the ecosystem community. Starting with a brief update and background on Imperas and the RISC-V activities, highlighting the processor models for software development and processor verification, leads on to the work within the Compliance working group including the RV32I suite announced at the RISC-V Summit in December 2019.

Plus, other verification activities based on working with customers on complex RISC-V implementations using the Imperas RISC-V Golden reference model.

The video can be viewed on the RISC-V YouTube channel here.

To see the video directly on YouTube, click here.