Accelerating a Cadence Platform Integration

Imperas’ processor models, including simulation and software design kit ToolMorphing™ technology, not only provides advanced capability with high-performance, but is an effective mechanism for the rapid integration of both model and tools into 3rd party platform realizations. This allows companies to perform all manner of integrations to suit end-user design scenarios.

Imperas’ processor models, including simulation and software design kit ToolMorphing™ technology, not only provides advanced capability with high-performance, but is an effective mechanism for the rapid integration of both model and tools into 3rd party platform realizations. This allows companies to perform all manner of integrations to suit end-user design scenarios.

Cadence made good use of this technology when creating a software and hardware design solution for the Xilinx Zynq™ -7000 SoC, centered on the Imperas processor models and M*SDK embedded software development environment.

The integration of the Imperas tools and OVP Fast Processor Models into the Cadence Virtual System Platform tool suite meant they could deliver an integrated efficient development environment based around Virtual Platforms to their customers.

Platform Modeling and Integration

Processor and Platform providers in general have a need to provide software models of their products as a significant value add to their offering. Such a model means that their device may be programmed more easily.

Some vendors go further, producing a complete set of tools to ensure that their IP can be utilized at its most effective. Many vendors will work with specialist tool and model companies to produce the required system, and Imperas has many partnerships of this nature.

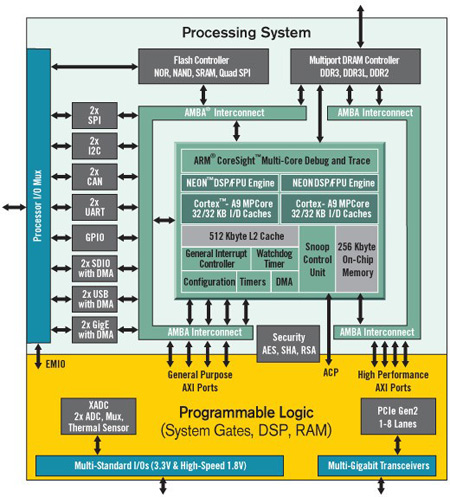

Cadence Design Systems, an EDA tool company, works with various silicon vendors to help them with their tool and model needs. In 2012 they formed a partnership with Xilinx to produce a model coupled with its own tool suite for their Zynq-7000 SoC, which is used to provide a dedicated processor platform coupled with an FPGA matrix for a number of applications.

The platform consists of a dual core ARM® Cortex™-A9 processor with memory, standard peripherals and the FPGA matrix for custom hardware, and is delivered with a bootable version of Linux and other software stacks.

Given the hardware and software aspects of a Zynq-based design, Cadence required a software development environment and processor models that could be combined with their own hardware design tools. For this they partnered with Imperas.

“High performance processor models are an important part of our virtual prototype solution,” noted Michal Siwinski, the Group Director for System Realization at Cadence Design Systems.

Imperas Technology, Made for Integration

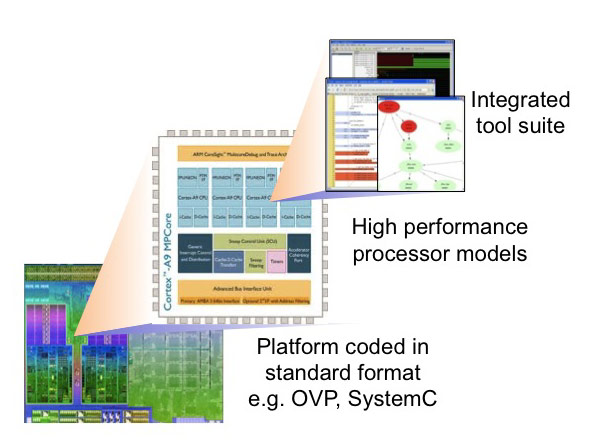

The Imperas system is unique in that it is centered around the processor model and simulation technology, with the development tools built in to this core, rather than the more traditional approach of separate, disparate components. This ToolMorphing™ technology leads to significant capability, performance and ease of use benefits. It also means that integrating a high-performance model with its embedded simulator and tooling is far more straightforward than with other approaches.

Imperas provides a broad range of processor models ready for integrating into a platform, which may be coded using various methods, including SystemC (with TLM2 interfaces), OVP, and straight forward C or C++. Once integrated, the user has the full benefit of the incorporated simulator and development tools. The development environment itself has also been constructed in such a way that custom tools may be written and added to it and its APIs may be used to provide integration into other tool suites. In the plug and play world of SoC modeling, the ability to integrate both model and design kit easily and with little performance impact, is both critical and rare.

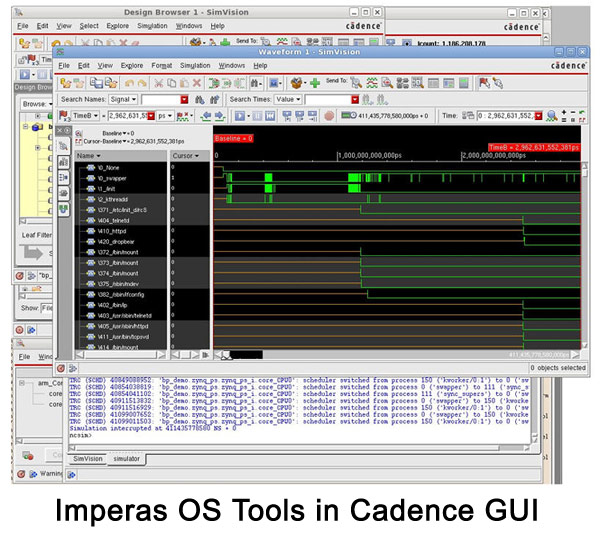

In addition, once the model and tool integration into the platform was complete, the next stage was to port Linux and other software stacks onto the processor, and the built-in Imperas tools were ideal for this purpose. Operating at the OS aware level, various capabilities were applied to quickly verify software operation, handling complex bugs that can be caused during the OS porting and customization process.

Cadence Integrated Solution for Xilinx End-Users

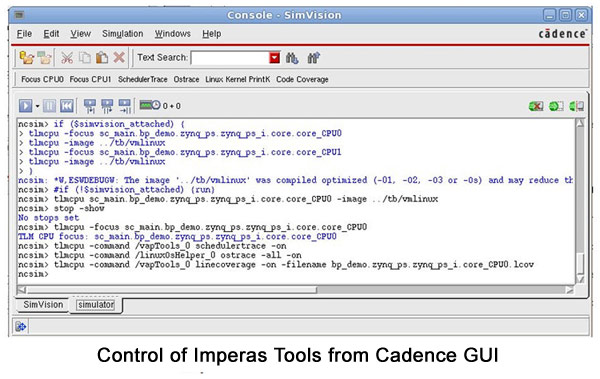

Cadence completed a SystemC representation of the Zynq platform, dropping in an Imperas model of the dual ARM Cortex-A9 with a SystemC TLM2 interface, complete with simulator and development environment. They also integrated the Imperas M*SDK software design kit with their own SimVision™ graphical hardware debug environment, enabling a multicore hardware software development system.

The entire development program required approximately 8 weeks.

The combined Cadence/Imperas tool/model integration partnership is now able to deliver a development system for Xilinx devices that allows software engineers to immediately commence the construction of their code in parallel with the hardware designers working on custom RTL to target the FPGA matrix. It is possible to debug the software and hardware together, while both are being coded, to ensure that the correct interaction is taking place with registers, interrupts, memory and other signaling.

Michal Siwinski of Cadence continued, “The Open Virtual Platforms library of fast processor core models, together with Imperas tools for software analysis, complement the [Cadence] Virtual System Platform to provide an effective solution for system and software development.”