Overview

Imperas is the industry leading developer of world class models and simulation technology of the most popular microprocessor ISAs, including Arm, MIPS, Power, and most recently RISC-V. Imperas products are used by many of the world’s leading semiconductor and systems companies.

For over 10 years customers have used Imperas models and technology as the reference for their software development and their hardware RTL Design Verification reference.

The introduction to the market of the ImperasDV product for the RISC-V processor market transforms the challenges that RISC-V users have in ensuring their products are high quality, very well tested, and adhere to the ISA specifications.

The Imperas RISC-V verification solution enables all RISC-V processor developers and users to perform highly complex hardware DV ‘out of the box’. Imperas brings what was a complex, highly proprietary, and hard to develop engineering technology for processor DV into the hands of all RISC-V developers.

The ImperasDV product is built on the very reliable and high quality processor modelling technology and simulation capabilities used by 100’s of users worldwide.

It is clear that every RISC-V processor developer needs help with verification and few RISC-V developers have the experience, technology, resources, or timescales to build their own solutions - hence ImperasDV - industrial quality RISC-V processor verification made easy.

ImperasDV enables full RISC-V processor hardware design verification to be completed to the highest quality levels demanded in the industry – and is available as a commercial product range with all the quality expected of high-end professional solutions. All that is required is model setup and DV configuration, along with integration into the customer’s RTL testbench.

ImperasDV works for standard RISC‑V processors and for custom designed architectures with interesting pipelines, microarchitecture, and custom extensions.

Introduction

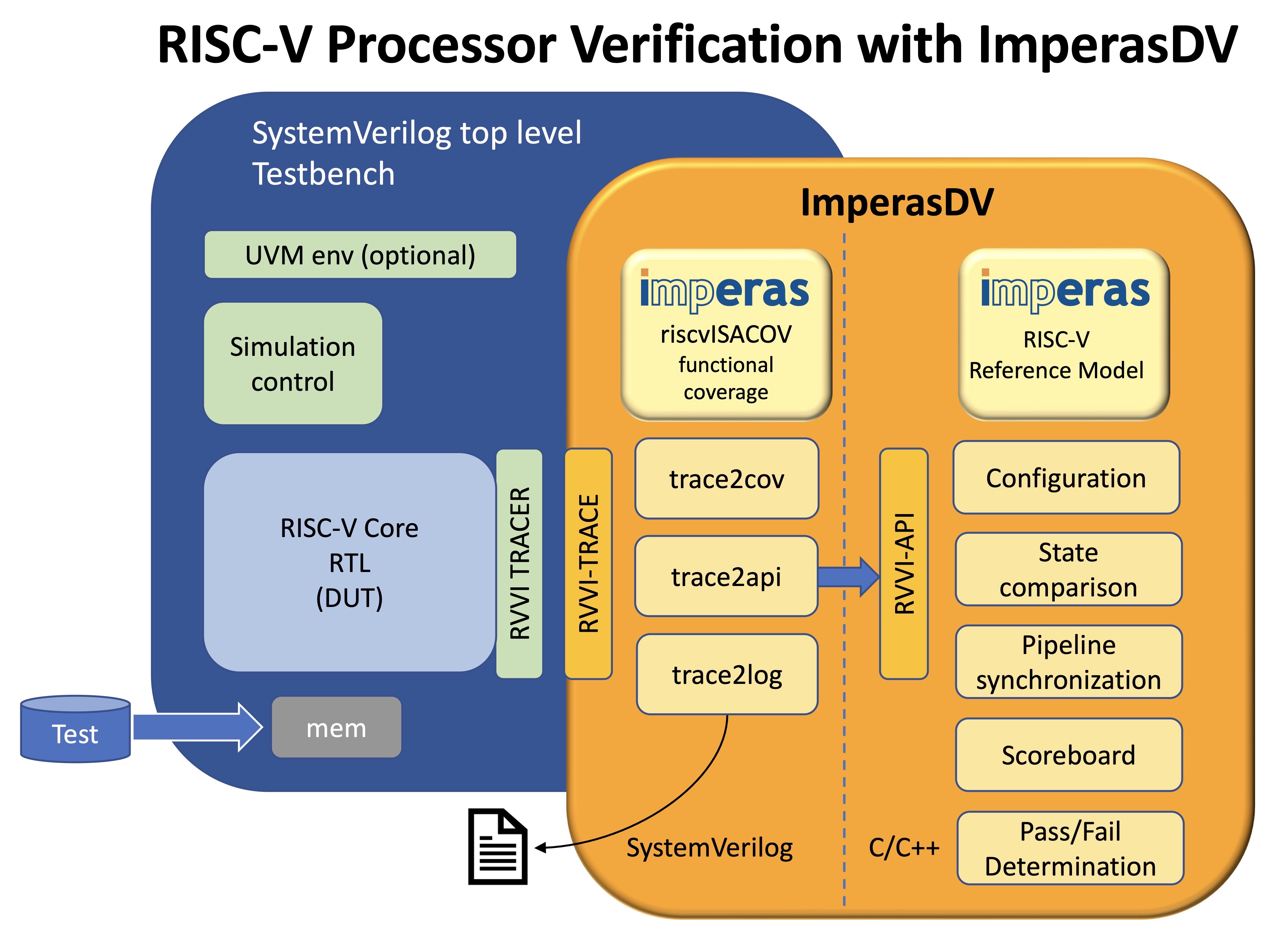

ImperasDV provides a sophisticated lock-step-compare hardware design verification environment that enables a Device Under Test (DUT) written in Verilog/SystemVerilog to execute (assembler) programs and at every architecturally visible event to have its operational data compared to the Imperas golden reference models to ensure correct operation.

There are several components in the ImperasDV product and there are several other components that are required in a complete functioning testbench.

These main components are:

- (random) instruction test generator

- RTL DUT subsystem

- Functional coverage measurement

- Test bench / harness

- Imperas DV subsystem

ImperasDV is a product from Imperas and a user needs to provide the other components - the test generator, the functional coverage, the RTL DUT and the test bench to bring it together.