Imperas Newsletter – January 2021

View this email in your browser

## RISC-V Reference Model for Processor DV

#### Latest news

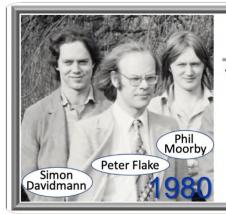

# Imperas reunites with SystemVerilog Co-Founders at DVCon 2021

'A personal perspective on the history of SystemVerilog / Superlog' with guest speakers:

Phil Moorby, inventor of Verilog HDL and Verilog-XL simulator

Peter Flake, inventor of HILO and Superlog, SystemVerilog

Simon Davidmann, HILO, Superlog, SystemVerilog

When: Tuesday March 2nd at 4pm PST

# Imperas reunites with SystemVerilog Co-Founders at DVCon 2021

As part of the participation at DVCon 2021, Simon Davidmann will host a personal perspective on the formation and history of SystemVerilog with Peter Flake and Phil Moorby, the developers of Verilog and SystemVerilog. The occasion is especially poignant as Imperas releases advanced SystemVerilog reference technology for RISC-V processor verification.

Tuesday March 2nd at 4pm PST

'A personal perspective on the history of SystemVerilog / Superlog'

Phil Moorby, inventor of Verilog HDL at Gateway Design Automation Inc.

Peter Flake, who developed Superlog at Co-Design Automation Inc.

Simon Davidmann, former CEO of Co-Design Automation Inc.

Learn more

#### **Events**

# Imperas at the virtual DVCon, March 1-4 2021

Online virtual event on the latest advances for RISC-V Verification with RISC-V Processor Reference Models and Verification IP

#### **Conference presentations**

'RISC-V Processor Verification: Case Study'

**NVIDIA Networking & Imperas**

Tuesday March 2nd at 3pm PST

'Jump start your RISC-V project with OpenHW'

OpenHW, Silicon Labs, Imperas, EM Microelectronic (part of Swatch Group)

Tuesday March 2nd at 3:30pm PST

#### **Conference Panel**

'Verification In The Open-Source Era'

SmartDV, Imperas, DARPA, Siemens EDA, Axiomise, Google

Wednesday March 3rd 8:30am - 9:30am PST

#### <u>Imperas sponsored sessions</u>

'25 years after Verisity, verification is still evolving'

**Bryan Dickman**, co-founder of Valytic, former ARM verification engineer and Specman user

Sean Smith of Esperanto, ex-Cisco DV lead, early Specman user

**Larry Lapides**, of Imperas and former vice president of worldwide sales at Verisity

Tuesday March 2nd at 2:30pm PST

'A personal perspective on the history of SystemVerilog / Superlog' Guest speakers include:

**Phil Moorby**, inventor of Verilog HDL at Gateway Design Automation Inc.

**Peter Flake**, who developed Superlog at Co-Design Automation Inc. **Simon Davidmann**, former CEO of Co-Design Automation Inc. Tuesday March 2nd at 4pm PST

'Advanced Processor verification in the era of open ISA's – is flexibility testing the limits of DV'

Featuring an overview of RISC-V Verification and resources.

Wednesday March 3rd at 2pm PST

#### Virtual Booth

Visit the virtual booth throughout the event to talk with the Imperas team on verification challenges to the open standard ISA of RISC-V.

# 01. - 05. March 2021 DIGITAL

# Imperas at virtual Embedded World, March 1-5 2021

Imperas Live presentation at the EW2021 Technical Conference:

'Software driven SoC Architectural Exploration for Al and ML accelerators with RISC-V'

Speaker: Simon Davidmann – Imperas Software When: Tuesday, March 2nd at 4:45pm CET

More information about this presentation can be found on <u>our website page</u>.

Virtual Exhibit: Visit the Imperas virtual booth and see all the latest demos and virtual platform technology for RISC-V Verification including custom instructions

and support for the latest RISC-V specifications for Vectors and Bit Manipulation. Set up a live 1-1 demo by clicking on the link below.

I'm ready to book a demo

# SAVE THE DATE: April 1 is OpenHW Day during RISC-V Week 2021

The "OpenHW Day" will present an interactive update on the CORE-V IP Cores, running projects and supporting infrastructure.

A detailed agenda to follow shortly.

# **Videos**

Watch video

Watch video

## **Articles**

Articles from

# **Big Changes In Verification**

High-quality and efficient verification requires a focus on details. Read more.

### When Is Verification Done?

The actual time may be more of a fuzzy risk assessment than a clear demarcation. Read more.

#### Release information

#### OVP and riscvOVPsim RELEASE NEWS

The latest Imperas and OVP release at the Open Virtual Platforms website.

For an introduction to RISC-V the free single core envelope model, called riscvOVPsim, is an excellent starting point, which can be configured for all the ratified ISA features and includes support of the draft specifications for Bit Manipulation and Vectors.

The latest version was uploaded on 26 February 2021, Version: 20210226.0 and is available via GitHub here.

The free enhanced riscvOVPsimPlus, including many more features including full configurable instruction trace, GDB/Eclipse debug, and memory configuration options, plus the RISC-V Vector and other test suites, is now available on the OVP website here.

riscvOVPsim, learn more

Has someone forwarded our newsletter to you? Join our mailing list.

#### This email was sent to << Email Address>>

why did I get this? unsubscribe from this list update subscription preferences

Imperas Software Limited · Imperas Buildings, North Weston · Thame, Oxfordshire OX92HA · United Kingdom