Imperas leading commercial simulation technology available for free with RISC-V Open Virtual Platform Simulator (riscvOVPsim™) for RISC-V software development, compliance and DV test developments

RISC-V Ecosystem comments from:

SiFive, Esperanto, Andes, Codasip, Syntacore, ETH Zurich, InCore, Bluespec

Oxford, United Kingdom, November 6, 2018 - Imperas Software Ltd., Oxford, United Kingdom, November 6, 2018 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today announced the RISC-V Open Virtual Platform Simulator (riscvOVPsim™) as a reference Instruction Set Simulator (ISS), including open source…

Brian Bailey of Simconductor Engineeringis considers open-source and the RISC-V ISA and discusses thr reuirement of continued industry support for it to be successful.

The open-source RISC-V instruction set architecture (ISA) is attracting a lot of attention across the semiconductor industry, but its long-term success will depend on levels of cooperation never seen before in the semiconductor industry. The big question now…

Imperas Accelerates Software Development, Debug and Test for Arm-based Embedded Systems

OXFORD, United Kingdom, September 12, 2018— Imperas Software Ltd., the leader in high-performance software simulation and virtual platforms, will exhibit at the 2018 ARM TechCon in booth #1023.

Imperas invites attendees to visit for a demonstration of Imperas embedded software development, debug and test solutions for Arm-based systems.

Demo Highlights:

…Simulation Models for Embedded Software and Smart Monitor IP Blocks

Multi-faceted Challenges of Embedded Software Development

We’re tackling the multi-faceted challenges of embedded software development in this week’s episode of Amelia’s Weekly Fish Fry.

Amelia Dalton of Electronic Engineering Journal takes a closer look at how debug environments can make all the difference in complex designs and why the RISC-V architecture is gaining traction. Simon Davidmann…

Imperas Virtual Platform, Software Simulator and Models for AndesCore N25 and NX25 Processors

Now Certified as a Reference by Andes Technology Corp.

Oxford, United Kingdom, June 21, 2018 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, and Andes Technology Corporation, the prominent CPU IP provider, today announced that Andes has certified the Open Virtual Platforms™ (OVP™) instruction-accurate models and virtual platforms of the…

Advanced debug environment for multicore processor designs used for both hardware and simulation

Cambridge, UK –21 June 2018 / DAC, San Francisco

UltraSoC and Imperas today announced a wide-ranging partnership that will provide developers of multicore systems on chip (SoCs) with a powerful combination of embedded analytics and virtual platform technologies. Under the terms of the agreement, UltraSoC will incorporate key elements of Imperas’ development…

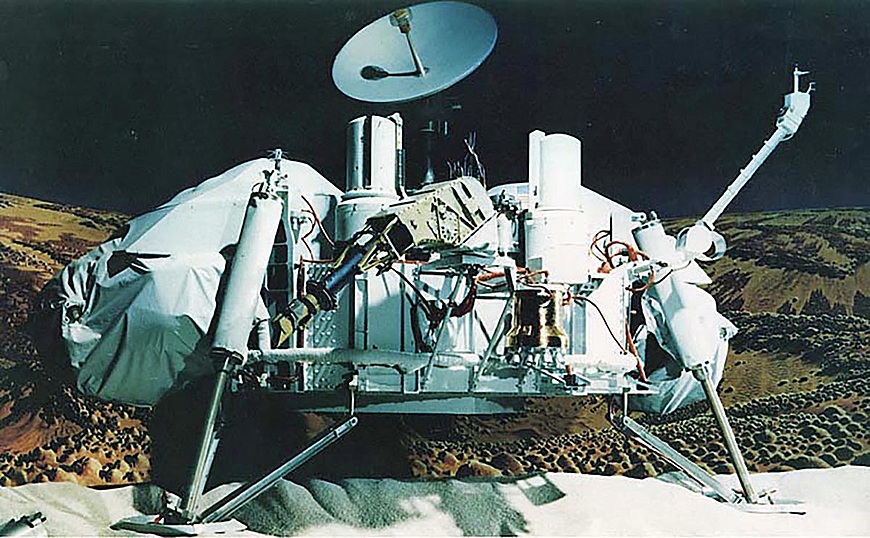

In the recent edition of Military Embedded Systems, Larry Lapides of Imperas, gives insights into work at JPL in the 70s and was there when the Viking landed on Mars. He writes about semiconductors, design teams, software releases, and simulation... and of course safety, securityand extra-functional features...

Shot of the Viking Lander. Courtesy NASA Space Science Data Coordinated Archive.

If you want to read the full article, click here.

##

AndeStar V5m Extensions for AndesCore N25 and NX25 Processors Now Supported by Imperas Virtual Platform Software Solutions and Models

Oxford, United Kingdom, May 1, 2018 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, and Andes Technology Corporation, today announced Open Virtual Platforms™ (OVP™) models and virtual platform support for powerful new extensions in the AndesCore™ N25 and NX25 IP processors, which are AndeStar™ V5 32-bit…

Highly efficient parallel processing, fast response to real-time events, and 50% performance gains position the I7200 as the core of choice for high performance embedded applications

Santa Clara, Calif. – May 1st, 2018 MIPS, provider of the widely used MIPS processor architecture and IP cores for licensing, today announced the I7200 multi-threaded multi-core processor, a new high performance licensable IP core in their midrange 32-bit product lineup. Class-leading efficiency is essential to power sensitive applications such as the high bandwidth modem…