In the recent edition of Military Embedded Systems, Larry Lapides of Imperas, gives insights into work at JPL in the 70s and was there when the Viking landed on Mars. He writes about semiconductors, design teams, software releases, and simulation... and of course safety, securityand extra-functional features...

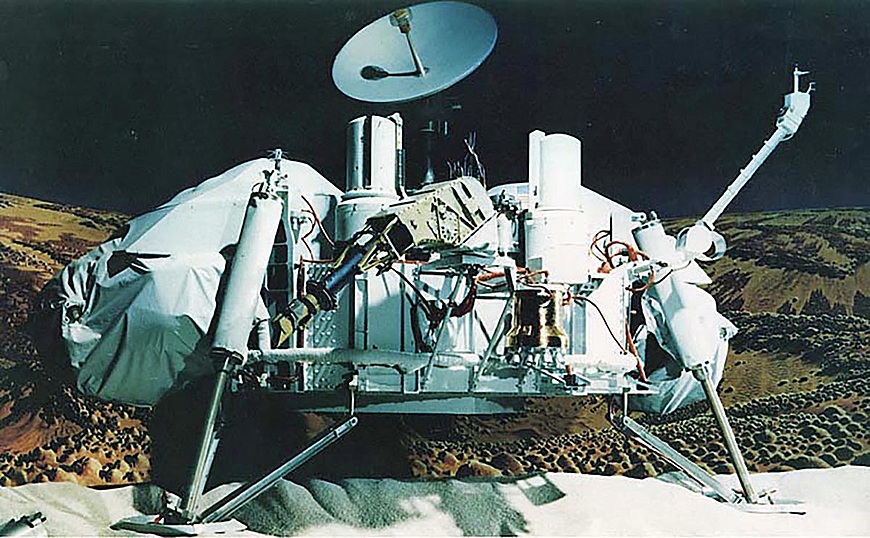

Shot of the Viking Lander. Courtesy NASA Space Science Data Coordinated Archive.

If you want to read the full article, click here.

##

AndeStar V5m Extensions for AndesCore N25 and NX25 Processors Now Supported by Imperas Virtual Platform Software Solutions and Models

Oxford, United Kingdom, May 1, 2018 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, and Andes Technology Corporation, today announced Open Virtual Platforms™ (OVP™) models and virtual platform support for powerful new extensions in the AndesCore™ N25 and NX25 IP processors, which are AndeStar™ V5 32-bit…

Highly efficient parallel processing, fast response to real-time events, and 50% performance gains position the I7200 as the core of choice for high performance embedded applications

Santa Clara, Calif. – May 1st, 2018 MIPS, provider of the widely used MIPS processor architecture and IP cores for licensing, today announced the I7200 multi-threaded multi-core processor, a new high performance licensable IP core in their midrange 32-bit product lineup. Class-leading efficiency is essential to power sensitive applications such as the high bandwidth modem…

Imperas Software, Ltd. formed part of the growing ecosystem of support for RISC-V, together with six other members, at the RISC-V Foundation booth at embedded world in Nuremberg, February- March 2018. Imperas featured a demo of the RISC-V virtual platform, showcasing both FreeRTOS and Linux booting.

Imperas presented two papers and took part in the exhibition. To read the article by Kevin McDermott in Embedded Computing Design, click here.

##

RISC-V Community Gets a Turnkey Software Solution Via Ashling/ Imperas Alliance

Embedded World 2018, Nuremburg, Germany–February 26, 2018. Ashling Systems (a subsidiary of the NeST Group) and Imperas Software today announced a partnership to provide integrated tools and solutions for RISC-V software development. The technology aspects of this alliance include the integration of Imperas’ high-performance virtual platforms, simulation engines and models into Ashling’s own RiscFree™ IDE…

A winning combination in delivering value to system developers

Paris, France - February 26th, 2018 - Since 2015, Magillem (www.magillem.com), the leading provider of front-end design xml solutions and best-in-class tools to reduce the global cost of

complex designs, has partnered with Imperas (www.imperas.com), which is revolutionizing embedded software development, debug and test for multi-core designs …

Despite its rich ecosystem and growing number of real-world implementations, misconceptions about RISC-V are keeping companies around the world from fully realizing its benefits.

Ted Marena of Microsemi has written an interesting article in Electronic Design about the RISC-V ecosystem.

Many companies today are exploring free, open-source hardware and software as an alternative to closed, costly instruction set architectures (ISAs).

RISC-V is a free, open, and extensible ISA that’s redefining the flexibility, scalability, extensibility, and modularity of…

Collaboration Enabled by Microsemi's Mi-V Ecosystem, Designed to Drive Adoption of FPGA-Based RISC-V Designs

Microsemi Corporation (Nasdaq: MSCC), a leading provider of semiconductor solutions differentiated by power, security, reliability and performance, and Imperas Software Ltd., the leader in high-performance software simulation and virtual platforms, today announced the Extendable Platform Kit™ for Microsemi Mi-V™ RISC-V soft central processing units (CPUs). The collaboration delivers the first commercially available…

Inflection point for RISC-V: The 7th RISC-V workshop in Silicon Valley

Imperas participated in the 7th RISC-V workshop in Milpitas, California, with a talk and demonstrations.

Each workshop has a different feel to it, and this one seems to be the inflection point in RISC-V maturity. Whereas past workshops felt a bit like a revival tent meeting, with most everyone caught up in the…