The actual time may be more of a fuzzy risk assessment than a clear demarcation.

Even with the billions of dollars spent on R&D for EDA tools, and tens of billions more on verification labor, only 30% to 50% of ASIC designs are first time right, according to Wilson Research Group and Siemens EDA.

Even then, these designs still have bugs. They’re just not catastrophic enough to cause a re-spin. This means more efficient verification is needed. Until…

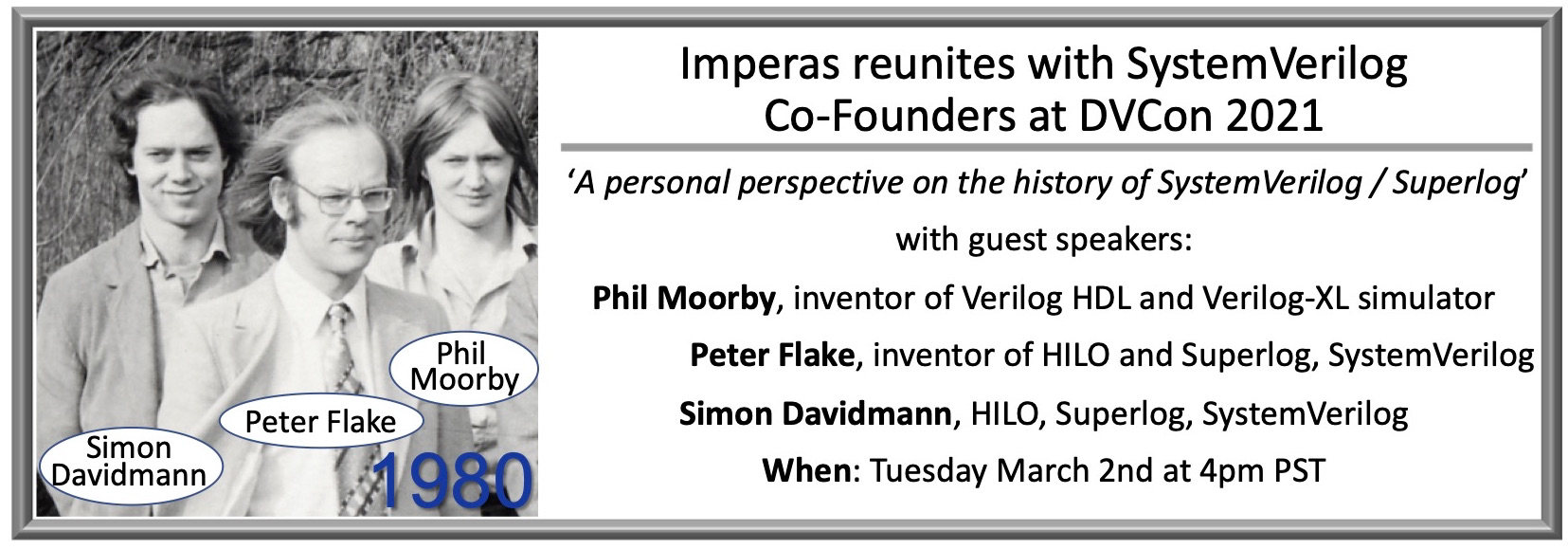

As Imperas releases advanced SystemVerilog reference technology for RISC-V processor verification it brings together Peter Flake, Simon Davidmann, and Phil Moorby to discuss their involvement in the creation of Verilog and SystemVerilog.

Oxford, UK – February 25th, 2021 – Imperas Software Ltd., the leader in RISC-V processor verification technology, today announced as part of the participation at DVCon 2021, Simon Davidmann…

The RISC-V ISA (Instruction Set Architecture) permits a range of possibilities for processor implementation with a modular approach for standard and custom extensions. In addition, implementations may be shared commercially or as open-source, and adopters beyond the original design team can use these directly or as a basis for further modifications and…

High-quality and efficient verification requires a focus on details.

Verification is undergoing fundamental change as chips become increasingly complex, heterogeneous, and integrated into larger systems.

Tools, methodologies, and the mindset of verification engineers themselves are all shifting to adapt to these new designs, although with so many moving pieces this isn’t always so easy to comprehend. Ferreting out bugs in a design now requires a multi-…

Verification IP extended with Floating-Point architectural validation test suites based on golden reference model and coverage-based development.

Oxford, UK – January 25th, 2021 – Imperas Software Ltd., the leader in RISC-V processor verification technology, today announced the latest addition to the Imperas RISC-V Verification IP (VIP) solutions with the Floating-Point architectural validation test suites covering the RISC-V…

The semiconductor industry will look and behave differently this year, and not just because of the pandemic.

The new year will be one of significant transition and innovation for the chip industry, but there are so many new applications and market segments that broad generalizations are becoming less meaningful. Unlike in years past, where sales of computers or smart phones were a good indication of how the chip industry would fare, end markets have both multiplied and…

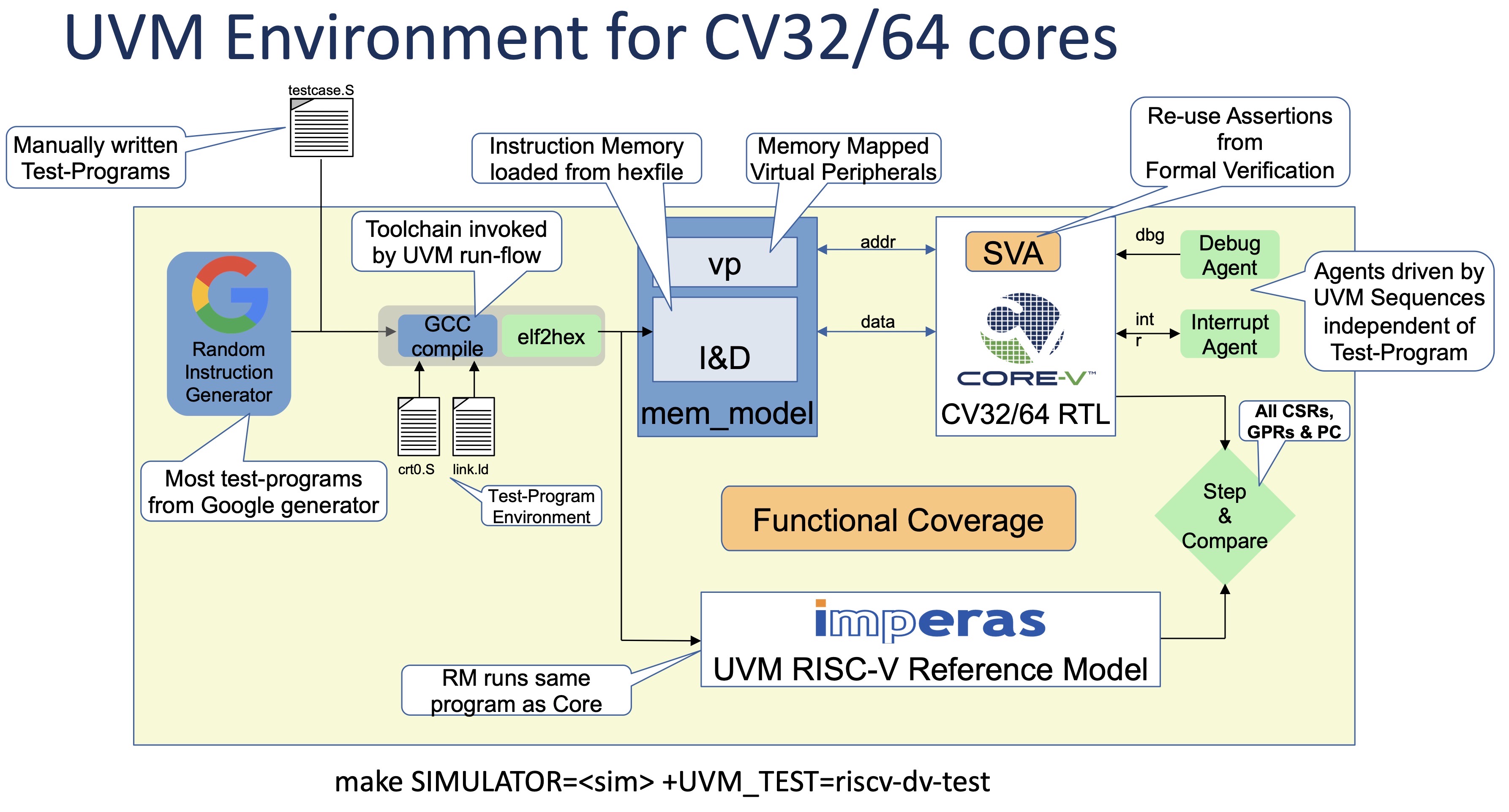

Using SoC methodologies for RISC-V processor DV.

As we celebrate over 50 years of microprocessors, the industry has embraced every generation of silicon process technology with architectural innovation plus new design methods that have supported innovations in almost every market segment. The interest around RISC-V is opening up increased activity around new approaches to optimize designs for the next generation of devices across multiple…

Complexity is making this process more difficult, but new and better approaches are being developed.

The proliferation and expansion of multicore architectures is making debug much more difficult and time-consuming, which in turn is increasing demand for more comprehensive system-level tools and approaches.

Multicore/multiprocessor designs are the most complex devices to debug. More interactions and interdependencies between cores mean…

The role of engineers is changing, and they need to be picking up new skills if they are to remain valuable team players. There are several directions they could go in.

Engineering has one constant — you innovate or fall by the wayside. That is true both for the things that are designed and for the engineers who design and build them. Today’s systems are putting new strains on engineers who can no longer be “tall and thin” or “short and fat.” Those descriptions…