The road to optimized tradeoff automation is long. Changing attributes along the way can make it even more difficult.

Complexity challenges long-held assumptions. In the past, the semiconductor industry thought it understood performance/area tradeoffs, but over time it became clear this is not so simple. Measuring performance is no longer an absolute. Power has many dimensions including peak, average, total energy and heat, and power and function are tied together.

Design teams are now dealing with the implication of safety and security, which have considerable impact on power/…

Showing that a processor core adheres to a specification becomes more difficult when the specification is extensible.

The open-standard RISC-V instruction set architecture (ISA) continues to gain momentum, but the flexibility of RISC-V creates a problem—how do you know if a RISC-V implementation fits basic standards and can play well with other implementations so they all can run the…

Experts at the Table: While attention is being paid to security in IoT devices, still more must be done.

Semiconductor Engineering sat down with Chris Jones, vice president of marketing at Codasip; Martin Croome, vice president of business development at GreenWaves Technologies; Kevin McDermott, vice president of marketing at Imperas; Scot Morrison, general manager, embedded platform technology at Mentor, a Siemens Business; Lauri Koskinen, CTO at Minima; and Mike Borza, principal security technologist at Synopsys. What follows are excerpts of that discussion…..

To read…

Bernard Murphy of SemiWiki is becoming more interested in developments in the RISC-V industry and has talked with Krste Asanovic of UCB and SiFive and with Imperas.

Compliance to the open-ISA standard is a big issue and Bernard talked with Kevin McDermott (VP Marketing at Imperas) to explore what is needed. Imperas' new free ISS, riscvOVPsim, a RISC-V compliance simulator is discussed.

…

Brian Bailey of Simconductor Engineeringis considers open-source and the RISC-V ISA and discusses thr reuirement of continued industry support for it to be successful.

The open-source RISC-V instruction set architecture (ISA) is attracting a lot of attention across the semiconductor industry, but its long-term success will depend on levels of cooperation never seen before in the semiconductor industry. The big question now…

Simulation Models for Embedded Software and Smart Monitor IP Blocks

Multi-faceted Challenges of Embedded Software Development

We’re tackling the multi-faceted challenges of embedded software development in this week’s episode of Amelia’s Weekly Fish Fry.

Amelia Dalton of Electronic Engineering Journal takes a closer look at how debug environments can make all the difference in complex designs and why the RISC-V architecture is gaining traction. Simon Davidmann…

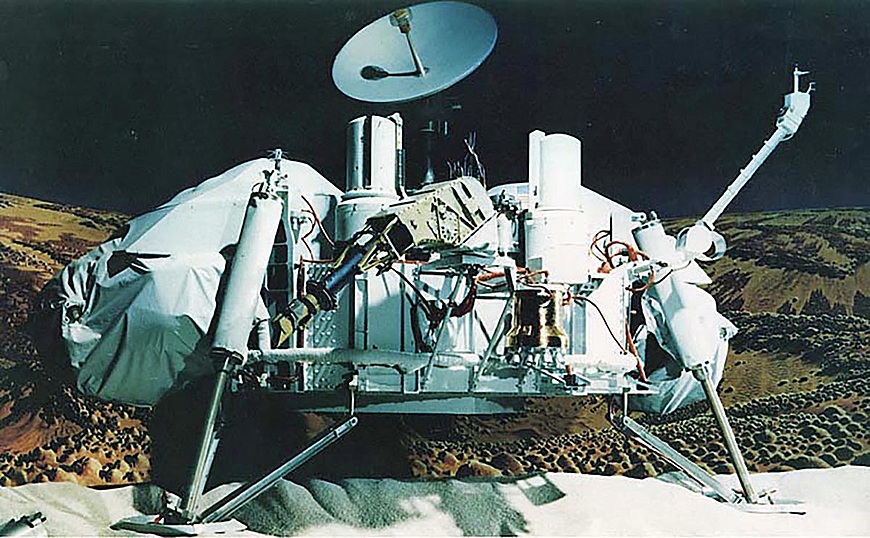

In the recent edition of Military Embedded Systems, Larry Lapides of Imperas, gives insights into work at JPL in the 70s and was there when the Viking landed on Mars. He writes about semiconductors, design teams, software releases, and simulation... and of course safety, securityand extra-functional features...

Shot of the Viking Lander. Courtesy NASA Space Science Data Coordinated Archive.

If you want to read the full article, click here.

##

Imperas Software, Ltd. formed part of the growing ecosystem of support for RISC-V, together with six other members, at the RISC-V Foundation booth at embedded world in Nuremberg, February- March 2018. Imperas featured a demo of the RISC-V virtual platform, showcasing both FreeRTOS and Linux booting.

Imperas presented two papers and took part in the exhibition. To read the article by Kevin McDermott in Embedded Computing Design, click here.

##