RISC-V Vector Instruction Extension for Automotive applications to be verified with Imperas leading proprietary code-morphing simulation technology, verification tools and validation suite

Oxford, United Kingdom, September 24th, 2020 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today confirmed the…

Building an open-source verification environment is not an easy or cheap task. It remains unclear who is willing to pay for it

Defining an open-source verification methodology is a lot more difficult than just developing an open-source simulator. This is the reality facing open-source hardware such as RISC-V. Some people may be asking for the corresponding open-source verification, but that is a much tougher problem — and it is not going to be…

The open specification of the RISC-V ISA (Instruction Set Architecture) permits a range of possibilities for processor implementation with a modular approach for standard and custom extensions. In addition, implementations may be shared commercially or as open source, and adopters beyond the original design team can use these directly or as a basis for further modifications…

Sorting out what is meant by open-source verification is not easy, but it leaves the door open to new approaches

Ask different people what open-source verification means and you will get a host of different answers. They range from the verification of open-source hardware, to providing an open-source verification infrastructure, to providing open-source stream generators or reference models, to open-source simulators and formal verification engines.

…

It has been an unusual DAC this year, as the show went virtual due to the Covid-19 pandemic. There was no exhibition floor as such, but there was a comprehensive programme of keynote speeches, presentations, tutorials and panel discussions

There was a lot of activity around RISC-V, including a presentation by Imperas Software (www.imperas.com) entitled ‘What’s Next for RISC-V? Vectors, Verification, and…

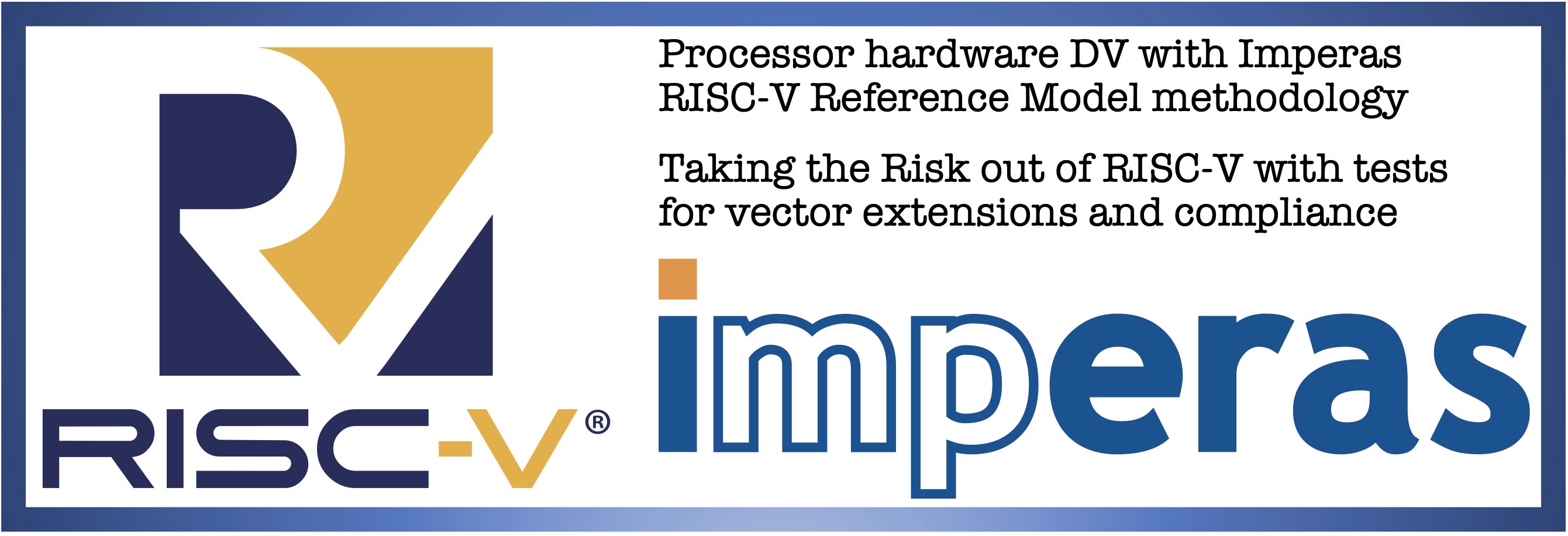

The OpenHW member-based verification team developing processor design verification test bench to validate open source cores in line with leading industry best practices

Oxford, United Kingdom, July 21st, 2020 — Imperas Software Ltd., the leader in virtual platforms and high-performance software simulation, today announced that OpenHW Group, the not-for-profit global organization set up to facilitate collaboration between hardware and…

The July 2020 edition of Mentor Graphics', a Siemens Business, Verification Horizons article and Verification Academy presentation on RISC-V Processor DV are now available online

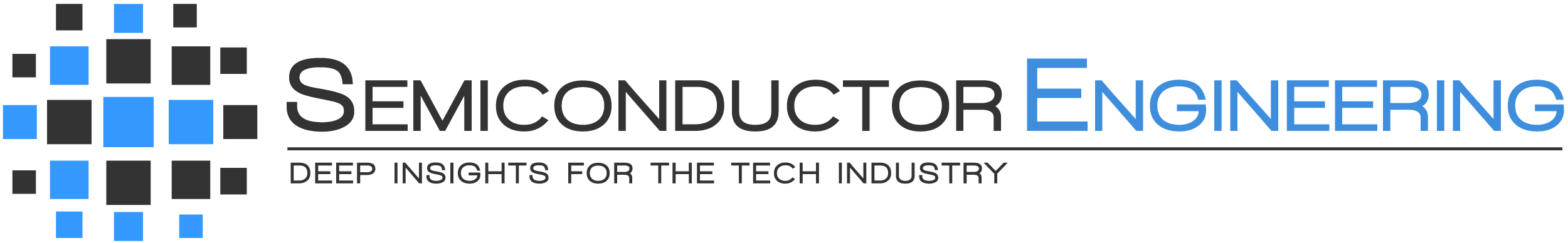

As SoC developers adopt RISC-V and the design freedoms that an Open ISA (Instruction Set Architecture) offers, DV teams will need to address the new verification challenges of RISC-V based…

RISC-V drives new attention to this market, but the cost/benefit equation is different for open-source hardware than software

Open-source hardware continues to gain ground, spearheaded by RISC-V — despite the fact that this processor technology is neither free nor simple to use.

Nevertheless, the open-source hardware movement has established a solid foothold after multiple prior forays that yielded only limited success, even for processors. With demand…

Recently Embedded Magazine published a very interesting article with some insights on extending a RISC-V processor with custom instructions

The open instruction set architecture (ISA) of RISC-V permits broad flexibility in implementation and offers optional features that can enable fresh approaches to resolving hardware-software design tradeoffs. Based on a modular structure, a number of standard extensions and options can be used to configure…