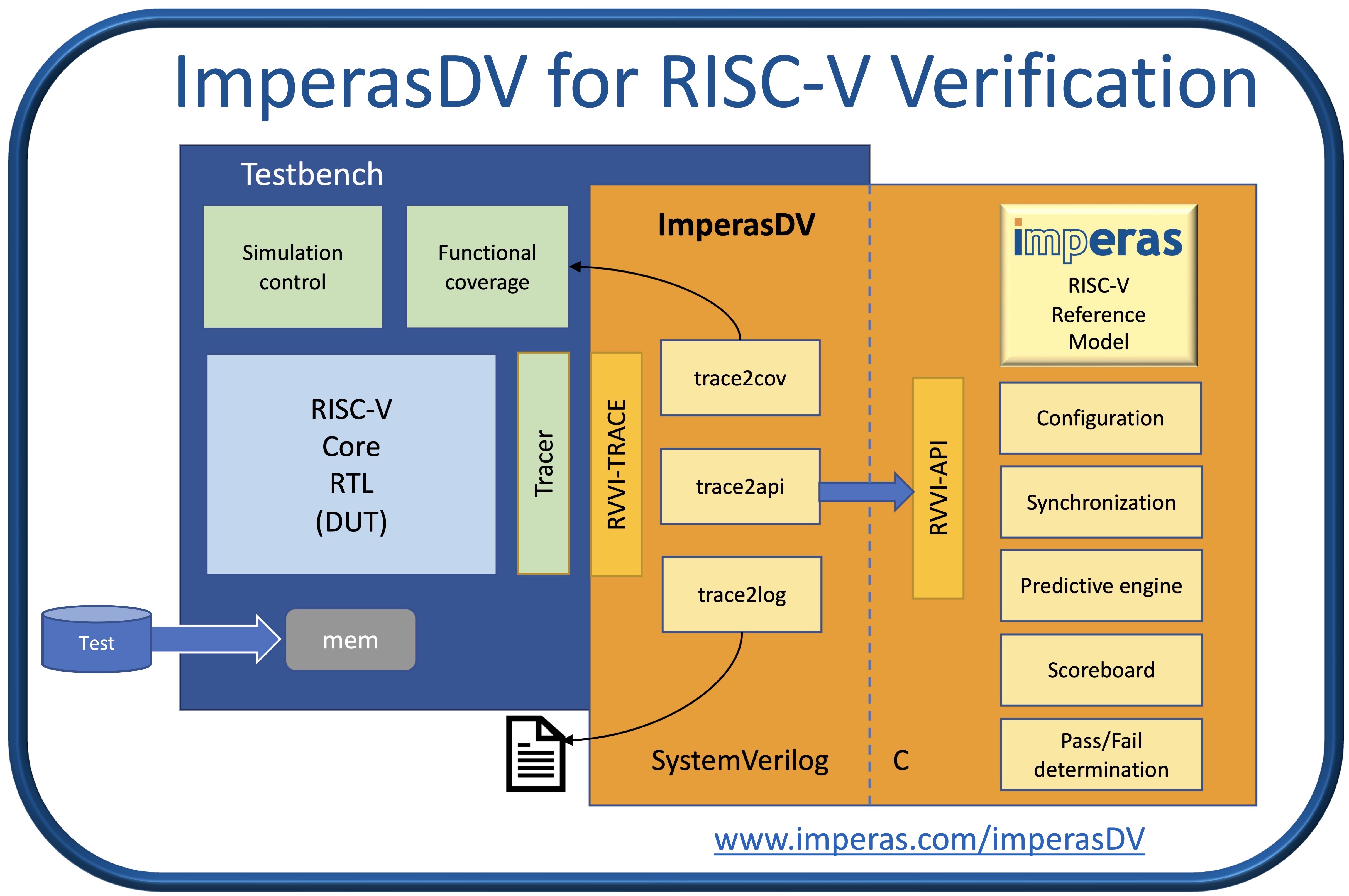

ImperasDV is based on the trusted Imperas reference models and Verification IP, combined with architectural validation test suites and coverage libraries, and with native RVVI support

Oxford, United Kingdom – December 12th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced the latest updates to ImperasDV to support the rapid growth in RISC-V verification as developers extend into…

Imperas reference model for IMG RTXM-2200 is available on request to lead customers for real-time embedded applications in next generation domain-specific SoCs

Oxford, United Kingdom – December 8th, 2022 – Imperas Software Ltd.,the leader in RISC-V simulation solutions, today announced that Imagination Technologies, a global technology leader in silicon IP (…

Building on 35 years of innovation in RISC processor development, MIPS’ strategic move to RISC-V is supported by Imperas RISC-V Reference Models, Verification IP, and test suites

Oxford, United Kingdom – December 7th, 2022 – Imperas Software Ltd.,the leader in RISC-V simulation solutions, announced today that MIPS, a leading developer of highly scalable RISC processor IP, has selected Imperas to provide advanced RISC-V…

Imperas leadership in the RISC-V Verification Ecosystem recognized in the expanded OpenHW Verification Task Group charter to lead the RISC-V community in adapting to the challenges of RISC-V processor verification

Oxford, United Kingdom – December 5th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced that Simon Davidmann has been elected as Chair of the OpenHW…

Imperas reference models for Andes expanded with Andes Custom Extension™ support and design flow integration for leading EDA environments, plus new AndesCore® N25F-SE core for functional safety applications

Oxford, United Kingdom – November 29th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced that Andes Technology Corp., a leading supplier of performance-efficient and extensible 32/64-bit RISC-V processor cores and…

New Integrated Development Environment for RISC-V includes Imperas simulator and reference model as a fixed platform kit for software development and architectural analysis

Oxford, United Kingdom – August 30th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced a strategic alliance with Intel®…

Complete source file access allows easy adoption and enables user extensions for advanced microarchitecture verification that helps all RISC-V projects accelerate time-to-market goals

Oxford, United Kingdom – August 2nd, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced the release of the first open-source…

Open Standard RISC-V Verification Interface (RVVI) extended with new configurable options for complex system level testing as a foundation for the RISC-V Verification Ecosystem

Oxford, United Kingdom – July 11th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced the latest updates for RVVI…

With a unified, standards-based approach to verification and Verification IP reusability, mutual customers can seamlessly transition between RISC-V processor and system level DV

Oxford, United Kingdom – July 7th, 2022 – Imperas Software Ltd., the leader in RISC-V simulation solutions, today announced a partnership with Breker Verification Systems, a leading…